# GOC-BE470-V1.1

# **Bluetooth Module Hardware Specification**

Document Type: Bluetooth Module Hardware Specification

Document Number: GOC-BE470-V1.1

Document Version: 1.7

Release Date: 2020/07/24

Mobile:15817435207 Bill

Fax:0755-29658104 TEL: 0755-29663177

Website:www.goodocom.com

Address:305, 3 / F, Xia Gu, Meisheng Huigu Science and Technology Industry Park, 83 Dabao Road, 33 District, Baoan District, Shenzhen City

# Copyright 2006~2020 by GOODOCOM Technologies SHENZHEN INC., All Right Reserved.

Be careful:

- 1. The module must use ladder steel net, and recommend ladder steel net thickness 0.16--0.20mm. The adaptability of the products is adjusted accordingly.

- 2. Before the use of the module, bake at 60 degrees centigrade and bake for 12 hours.

# **Release Record**

| Version Number | Release Date | Contents                                 |

|----------------|--------------|------------------------------------------|

| 1.0            | 2017/01/05   | Initial draft                            |

| 1.1            | 2017/05/11   | Increase module detail size              |

| 1.2            | 2017/07/11   | Update Bluetooth Standard                |

| 1.3            | 2018/08/01   | Update Bluetooth Standard                |

| 1.4            | 2018/09/20   | Increase echo cancellation               |

| 1.5            | 2019/05/09   | Update reference design                  |

| 1.6            | 2019/08/07   | Increase packing methods and performance |

|                |              | parameters, Cancel reference design      |

| 1.7            | 2020/07/24   | Increase Power Sequence                  |

# **Contents**

| 1. Introduction                                  | 4  |

|--------------------------------------------------|----|

| 1.1 System Block Diagram                         | 4  |

| 1.2 Features                                     | 4  |

| 1.2.1 Transmit And Receive Functions             | 5  |

| 1.2.2 Bluetooth 5.0 + EDR Features               |    |

| 1.3 Applications                                 | 5  |

| 2. Main Specification                            |    |

| 3. Pin Diagram And Description                   | 6  |

| 3.1 Pin Diagram                                  | 6  |

| 3.2 Pin Description                              |    |

| 3.3 PCB Layout Footprint                         | 8  |

| 4. Approximate Dimensions of Inverted-F Antenna  | 8  |

| 5. RF Interface                                  | 9  |

| 6. Power Sequence                                | 9  |

| 6.1 Power On Sequence                            | 9  |

| 6.2 Power Down Sequence                          | 9  |

| 7. Peripheral Transport Unit                     | 10 |

| 7.1 PCM Interface                                | 10 |

| 7.1.1 System Diagram                             | 10 |

| 7.1.2 Slot Mapping                               | 11 |

| 7.1.3 Wideband Speech7.1.4 Frame Synchronization | 11 |

| 7.1.4 Frame Synchronization                      | 11 |

| 7.1.5 Data Formatting                            | 11 |

| 7.2 UART Interface                               | 12 |

| 7.3 LPO Clock Interface                          | 12 |

| 8. UART Timing                                   | 12 |

| 8. UART Timing                                   | 13 |

| 10. Recommended Reflow Profile                   | 16 |

| 11. Electrical Characteristics                   | 17 |

| 11.1 Absolute Maximum Ratings                    | 17 |

| 11.2 Recommended Operating Conditions            | 17 |

| 12. PCB Layout Recommendation                    |    |

| 12.1 Antenna                                     | 17 |

| 12.2 HCI UART Lines Layout Guideline             |    |

| 12.3 PCM Lines Layout Guideline                  |    |

| 12.4 Power Trace Lines Layout Guideline          |    |

| 12.5 Ground Lines Layout Guideline               |    |

| 13. Echo Cancellation Principle                  |    |

| 14. Module Part Number Description               | 18 |

| 15. Ordering Information                         |    |

| 16. Packaging Information                        |    |

| 16.1 Net Weight                                  |    |

| 16.2 Package                                     |    |

| 16.3 Storage Requirements                        | 19 |

| 16.4 Humidity Sensitive Characteristic           | 19 |

#### 1. Introduction

The GOC-BE470-V1.1 is a monolithic, Bluetooth 5.0+EDR+BLE compliant, stand-alone baseband processor with an integrated 2.4GHz transceiver. Manufactured using the industry's most advanced 40nm CMOS low-power process, the GOC-BE470-V1.1 employs the highest level of integration, eliminating all critical external components, and thereby minimizing the device's footprint and costs associated with the implementation of Bluetooth solutions.

The GOC-BE470-V1.1is the optimal solution for voice and data applications that require a Bluetooth SIG standard Host Controller Interface (HCI) via UART H4, and PCM audio interface support.

The GOC-BE470-V1.1 transceiver's enhanced radio performance meets the most stringent industrial temperature application requirements for compact integration into mobile handset and portable devices. The GOC-BE470-V1.1 provides full radio compatibility, enabling it to operate simultaneously with GPS and cellular radios.

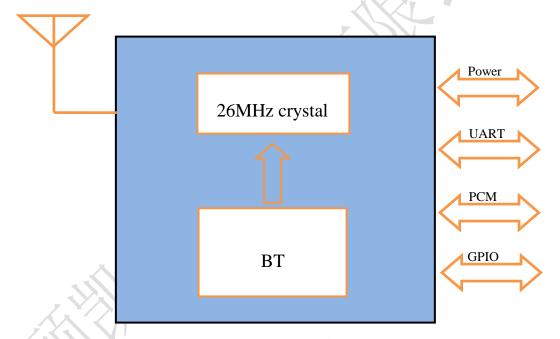

#### 1.1 System Block Diagram

Figure 1: GOC-BE470-V1.1 System Block Diagram

#### 1.2 Features

- Bluetooth 5.0 + EDR compliant.

- Class 1 capable with built-in PA.

- Programmable output power control meets Class 1, Class 2 requirements.

- Use supply voltages up to 3.3V.Supports Cypress SmartAudio®, wide-band speech, SBC codec, and packet loss concealment.

- Fractional-N synthesizer supports frequency references from 12 MHz to 52 MHz.

- Automatic frequency detection for standard crystal and TCXO values when an external 32.768 kHz reference clock is provided.

- Ultra-low power consumption.

- Supports serial flash interfaces.

- ARM7TDMI-S—based microprocessor with integrated ROM and RAM.

- Supports patch RAM download without external memory.

#### 1.2.1 Transmit And Receive Functions

The following transmit and receive functions are implemented in the BBC hardware to increase the reliability and security of the TX/RX data before sending the data over the air: In the transmitter:

#### Data framing:

- Forward error correction (FEC) generation

- Header error control (HEC) generation

- Cyclic redundancy check (CRC) generation

- Key generation

- Data encryption

- Data whitening

#### In the receiver:

- Symbol timing recovery

- Data deframing

- FEC

- HEC

- CRC

- Data decryption

- Data dewhitening

#### 1.2.2 Bluetooth 5.0 + EDR Features

The GOC-BE470-V1.1 supports Bluetooth5.0 + EDR, including the following options:

- Whitelist size of 25

- Enhanced Power Control

- HCI Read Encryption Key Size command

The GOC-BE470-V1.1 provides full support for Bluetooth 2.1 + EDR additional features:

- Secure simple pairing (SSP)

- Encryption pause resume (EPR)

- Enhance inquiry response (EIR)

- Link supervision time out (LSTO)

- Sniff subrating (SSR)

- Erroneous data (ED)

- Packet boundary flag (PBF)

#### 1.3 Applications

- Automotive handsfree radios

- Automotive data communication

- Industrial appliances

# 2. Main Specification

| BE470-V1.1<br>oth V5.0+EDR+BLE                             |

|------------------------------------------------------------|

| oth V5 0+EDR+BLE                                           |

| oth vs.ovebribee                                           |

| 48GHz                                                      |

| 、π/4 DQPSK、8DPSK                                           |

| hronous: 723.2kbps/57.6kbps<br>conous: 433.9kbps/433.9kbps |

|                                                            |

| Нор                             | 1600hops/sec, 1MHz channel space                |

|---------------------------------|-------------------------------------------------|

| Output impedance                | 50 ohms                                         |

| Crystal Frequency               | 26MHz                                           |

| Out interface                   | Power,UART,PCM                                  |

| Apply to Bluetooth instructions | A2DP, AVRCP,PAN,PBAP,HID,GATT,BLE,FTP,HS/HF,SPP |

| Range for working distance      | 10 meters (33 files)                            |

| Receiving Sensitivity           | -90dBm                                          |

| Out power                       | <10 dBm                                         |

| Connect Method                  | Point to Multi-Point                            |

| Dimension                       | 15.94*16.04*2.0mm                               |

| POWER Voltage                   | 3.3V supply voltage                             |

| Working Current                 | <44mA                                           |

| Standby Current                 | <730uA                                          |

| Working Temperature             | -40 ℃ to +85 ℃                                  |

| Storage Temperature             | -40 ℃ to +125 ℃                                 |

| Humidity Range                  | 10%~90% Non-Condensing                          |

Table 1: Main Specifications

# 3. Pin Diagram And Description

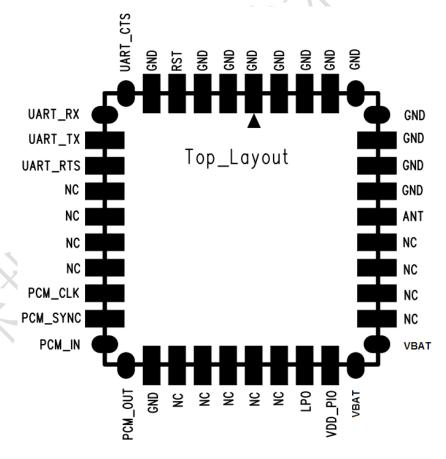

## 3.1 Pin Diagram

Figur 2: GOC-BE470-V1.1 Pin Diagram

# 3.2 Pin Description

| NO. | Pin name | I/O                                 | Description                      |

|-----|----------|-------------------------------------|----------------------------------|

| 1   | GND      | GND                                 | Ground connections               |

| 2   | GND      | GND                                 | Ground connections               |

| 3   | GND      | GND                                 | Ground connections               |

| 4   | RST      | Input                               | Active-low reset input           |

| 5   | GND      | GND                                 | Ground connections               |

| 6   | UART_CTS | Bidirectional with strong pull-down | UART clear to send, active low   |

| 7   | UART_RX  | Bidirectional with weak pull-up     | UART data input                  |

| 8   | UART_TX  | Bidirectional with weak pull-up     | UART data output                 |

| 9   | UART_RTS | Bidirectional with strong pull-down | UART request to send, active low |

| 10  | NC       | NC                                  | Leaves unconnected               |

| 11  | NC       | NC                                  | Leaves unconnected               |

| 12  | NC       | NC                                  | Leaves unconnected               |

| 13  | NC       | NC                                  | Leaves unconnected               |

| 14  | PCM_CLK  | Bidirectional with weak pull-down   | PCM synchronous data clock       |

| 15  | PCM_SYNC | Bidirectional with weak pull-down   | PCM synchronous data sync        |

| 16  | PCM_IN   | Bidirectional with weak pull-down   | PCM synchronous data input       |

| 17  | PCM_OUT  | Bidirectional with weak pull-down   | PCM synchronous data output      |

| 18  | GND      | GND                                 | Ground connections               |

| 19  | NC       | NC                                  | Leaves unconnected               |

| 20  | NC       | NC                                  | Leaves unconnected               |

| 21  | NC       | NC                                  | Leaves unconnected               |

| 22  | NC       | NC                                  | Leaves unconnected               |

| 23  | NC       | NC                                  | Leaves unconnected               |

| 24  | LPO      | Input                               | Slow clock. 32.768k              |

| 25  | VDD_PIO  | Power                               | 1.8~3.3V Supply voltage          |

| 26  | VBAT     | Power                               | 3.3V Supply voltage              |

| 27  | VBAT     | Power                               | 3.3V Supply voltage              |

| 28  | NC       | NC                                  | Leaves unconnected               |

| 29  | NC       | NC                                  | Leaves unconnected               |

| 30  | NC       | NC                                  | Leaves unconnected               |

| 31  | NC       | NC                                  | Leaves unconnected               |

|     |          |                                     | Bluetooth50Ωtransmitter          |

| 32  | ANT      | RF                                  | output/receiver input            |

| 33  | GND      | GND                                 | Ground connections               |

| 34  | GND      | GND                                 | Ground connections               |

| 35  | GND      | GND                                 | Ground connections               |

| 36  | GND      | GND                                 | Ground connections               |

| 37  | GND      | GND                                 | Ground connections               |

| 38  | GND      | GND                                 | Ground connections               |

| 39  | GND      | GND                                 | Ground connections               |

| 40  | GND      | GND                                 | Ground connections               |

Table 2: Pin Description

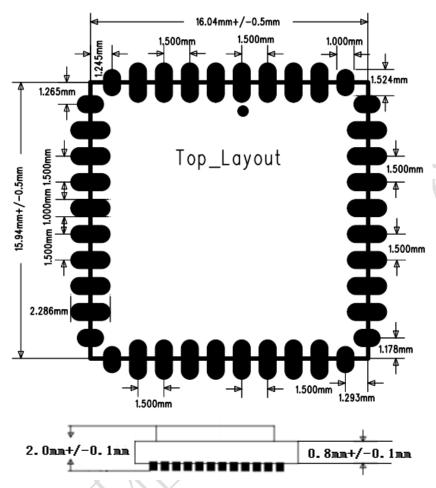

## 3.3 PCB Layout Footprint

Figure 3: PCB Layout Footprint

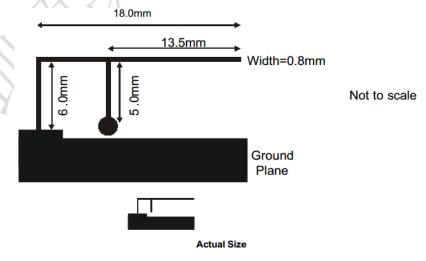

# 4. Approximate Dimensions of Inverted-F Antenna

Figure 4: Approximate Dimensions of Inverted-F Antenna

Special attention:

- 1. The position of the Bluetooth module is as far as possible not to walk the line and to lay the copper, especially in the vicinity of the antenna position.

- 2.Usually the Bluetooth module of the antenna as close to the edge of the PCB position, PCB antenna position slot.

- 3. In order to make the antenna performance in good condition, the antenna transmission line as far as possible in a straight line, the antenna on the top or bottom, do not play over the hole, the antenna and the distance between the laying of copper is greater than two times the normal spread of copper

- 4. Antenna transmission line to the length of the line should be as short as possible, should go to the surface, the length of the antenna is generally 30mm.

#### 5. RF Interface

The module integrates a balun filter. A 50ohms load is needed.

#### 6. Power Sequence

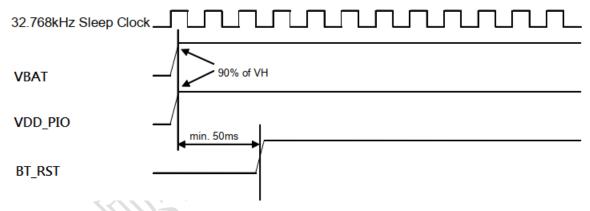

#### 6.1 Power On Sequence

VBAT should not raise 10%-90% faster than 40 microseconds or slower than 10milliseconds.

VBAT should be up before or at the same time as VDD\_PIO. VDD\_PIO should NOT be present fast or be held high before VBAT is high.

BT\_RST should be up after sleep clock oscillation is stabilized.

Please keep repeats power off sequence and power on sequence several times until it started normally.

Figure 5: Power On Sequence

#### Note

- 1) The GOC-BE470-V1.1 has an internal Power-on reset (POR) circuit. The device will be held in reset for a maximum of 110 ms after VBAT and VDD\_PIO have both passed the POR threshold. Wait at least 150 ms after VBAT and VDD PIO are available before initiating UART accesses.

- 2) VBAT should not rise 0% faster than 40 microseconds. VBAT should be up before or at the same time as VDD\_PIO should NOT be present first or be held high before VBAT is high.

- 3) After VBAT/VDD\_PIO is turned off, keep VBAT/VDD\_PIO OFF for at least 30 ms until next VBAT/VDD\_PIO ON.

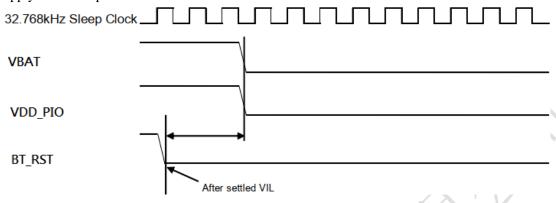

#### 6.2 Power Down Sequence

VDD\_PIO should be down before or at the same time as VBAT. VBAT should NOT be down earlier than VDD PIO low.

VDD PIO becomes low state is prior to VBAT low.

VBAT and VDD\_PIO should be down after BT\_RST are low. Waiting time from RST down to power supply off is not prescribed.

Figure 6: Power Down Sequence

# 7. Peripheral Transport Unit

This section discusses the PCM, UART, and SPI peripheral interfaces. The GOC-BE470-V1.1 has a 1040 byte transmit and receive FIFO, which is large enough to hold the entire payload of the largest EDR BT packet (3-DH5).

#### 7.1 PCM Interface

The GOC-BE470-V1.1 PCM interface can connect to linear PCM codec devices in master or slave mode. In master mode, the device generates the PCM\_CLK and PCM\_SYNC signals. In slave mode, these signals are provided by another master on the PCM interface as inputs to the device.

The device supports up to three SCO or eSCO channels through the PCM interface and each channel can be independently mapped to any available slot in a frame.

The host can adjust the PCM interface configuration using vendor-specific HCI commands or it can be setup in the configuration file.

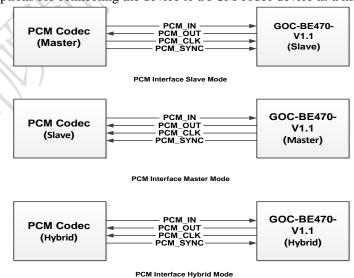

#### 7.1.1 System Diagram

Figure 7 shows options for connecting the device to a PCM codec device as a master or a slave.

Figure 7: PCM Interface with Linear PCM Codec

#### 7.1.2 Slot Mapping

The device supports up to three simultaneous, full-duplex SCO or eSCO channels. These channels are time-multiplexed onto the PCM interface using a time slotting scheme based on the audio sampling rate, as described in Table 5.

| <b>Audio Sample Rate</b> | Time Slotting Scheme                                                    |

|--------------------------|-------------------------------------------------------------------------|

|                          | The number of slots depends on the selected interface rate, as follows: |

|                          | Interface rate Slot                                                     |

|                          | 128 1                                                                   |

| 8 kHz                    | 256 2                                                                   |

|                          | 512 4                                                                   |

|                          | 1024 8                                                                  |

|                          | 2048 16                                                                 |

|                          | The number of slots depends on the selected interface rate, as follows: |

|                          | Interface rate Slot                                                     |

| 16 kHz                   | 256 1                                                                   |

| 10 KHZ                   | 512 2                                                                   |

|                          | 1024 4                                                                  |

|                          | 2048 8                                                                  |

Table 5: PCM Interface Time Slotting Scheme

Transmit and receive PCM data from an SCO channel is always mapped to the same slot. The PCM data output driver tristates its output on unused slots to allow other devices to share the same PCM interface signals. The data output driver tristates its output after the falling edge of the PCM clock during the last bit of the slot.

#### 7.1.3 Wideband Speech

The GOC-BE470-V1.1 provides support for wideband speech (WBS) in two ways:

- Transparent mode: The host encodes WBS packets and the encoded packets are transferred over the PCM bus for SCO or eSCO voice connections. In Transparent mode, the PCM bus is typically configured in master mode for a 4 kHz sync rate with 16-bit samples, resulting in a 64 kbps bit rate.

- On-chip SmartAudio® technology: The GOC-BE470-V1.1 can perform Subband-Codec (SBC) encoding and decoding of linear 16 bits at 16 kHz (256 kbps rate) transferred over the PCM bus.

#### 7.1.4 Frame Synchronization

The device supports both short and long frame synchronization types in both master and slave configurations. In short frame synchronization mode, the frame synchronization signal is an active-high pulse at the 8 kHz audio frame rate (which is a single bit period in width) and synchronized to the rising edge of the bit clock. The PCM slave expects PCM\_SYNC to be high on the falling edge of the bit clock and the first bit of the first slot to start at the next rising edge of the clock. In the long frame synchronization mode, the frame synchronization signal is an active-high pulse at the 8 kHz audio frame rate. However, the duration is 3-bit periods and the pulse starts coincident with the first bit of the first slot.

#### 7.1.5 Data Formatting

The device can be configured to generate and accept several different data formats. The device uses 13 of the 16 bits in each PCM frame. The location and order of these 13 bits is configurable to support various data formats on the PCM interface. The remaining three bits are ignored on the input, and may be filled with zeros, ones, a sign bit, or a programmed value on the output. The default format is 13-bit two's complement data, left justified, and clocked most significant bit first.

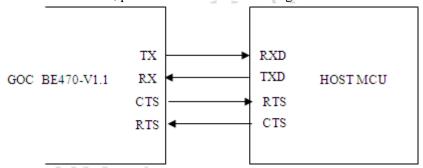

#### 7.2 UART Interface

The UART physical interface is a standard, 4-wire interface (RX, TX, RTS, CTS) with adjustable baud rates from 9600 bps to 4.0 Mbps. The interface features an automatic baud rate detection capability that returns a baud rate selection. Alternatively, the baud rate can be selected via a vendor-specific UART HCI command. The interface supports Bluetooth UART HCI (H4) specifications. The default baud rate for H4 is 115.2 Kbaud.

The following baud rates are supported:

| ■ 9600        | ■ 115200         | ■ 2000000 |

|---------------|------------------|-----------|

| <b>1</b> 4400 | <b>230400</b>    | ■ 3000000 |

| <b>19200</b>  | <b>460800</b>    | ■ 3250000 |

| ■ 28800       | <b>9</b> 21600   | ■ 3692000 |

| ■ 38400       | <b>■</b> 1444444 | ■ 4000000 |

| <b>57600</b>  | <b>1500000</b>   |           |

Table 6: Example of Common Baud Rates

Normally, the UART baud rate is set by a configuration record downloaded after reset or by automatic baud rate detection. The host does not need to adjust the baud rate. Support for changing the baud rate during normal HCI UART operation is provided through a vendor-specific command.

The GOC-BE470-V1.1 UART operates with the host UART correctly, provided the combined baud rate error of the two devices is within  $\pm 2\%$ .

When connecting the module to a host, please make sure to follow Figure 6.

Figure 8: GOC-BE470-V1.1 and HOST MCU use UART interface

#### 7.3 LPO Clock Interface

The LPO clock is the second frequency reference that the GOC-BE470-V1.1 uses to provide low-power mode timing for park, hold, and sniff.

The LPO clock can be provided to the device externally, from a 32.768 kHz source or the GOC-BE470-V1.1 can operate using the internal LPO clock.

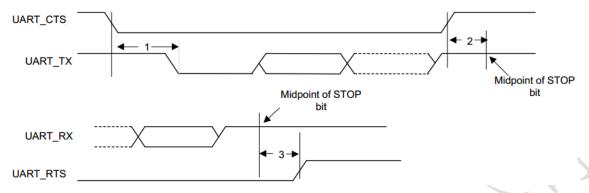

## 8. UART Timing

| Reference | Characteristics                                       | Minimum | Maximum | Unit           |

|-----------|-------------------------------------------------------|---------|---------|----------------|

| 1         | Delay time, UART_CTS low to UART_TX valid             | _       | 24      | Baudout cycles |

| 2         | Setup time, UART_CTS high before midpoint of stop bit | _       | 10      | ns             |

| 3         | Delay time, midpoint of stop bit to UART_RTS high     | _       | 2       | Baudout cycles |

**Table 7: UART Timing Specifications**

Figure 9: UART Timing

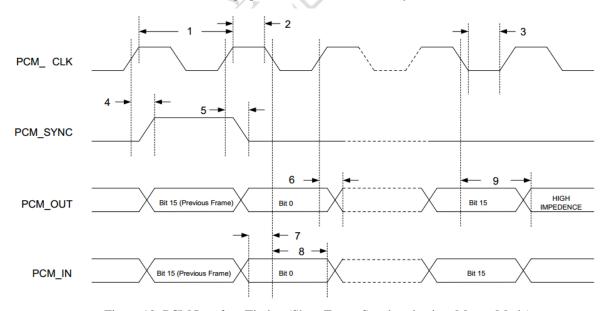

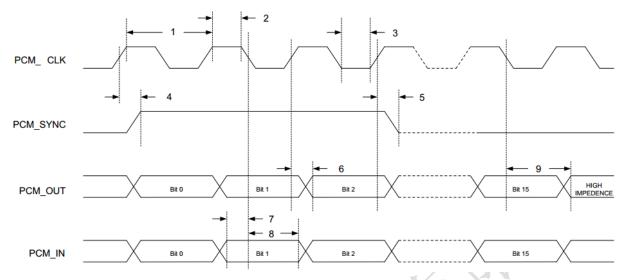

## 9. PCM Interface Timing

| Reference | Characteristics                                                                              | Minimum    | Maximum | Unit |

|-----------|----------------------------------------------------------------------------------------------|------------|---------|------|

| 1         | PCM bit clock frequency                                                                      | 128        | 2048    | kHz  |

| 2         | PCM bit clock HIGH time                                                                      | 128        | _       | ns   |

| 3         | PCM bit clock LOW time                                                                       | 209        | _       | ns   |

| 4         | Delay from PCM_CLK rising edge to PCM_SYNC high                                              | <i>λ</i> – | 50      | ns   |

| 5         | Delay from PCM_CLK rising edge to PCM_SYNC low                                               | _          | 50      | ns   |

| 6         | Delay from PCM_CLK rising edge to data valid on PCM_OUT                                      | _          | 50      | ns   |

| 7         | Setup time for PCM_IN before PCM_CLK falling edge                                            | 50         | _       | ns   |

| 8         | Hold time for PCM_IN after PCM_CLK falling edge                                              | 10         | _       | ns   |

| 9         | Delay from falling edge of PCM_CLK during last bit period to PCM_OUT becoming high impedance | _          | 50      | ns   |

Table 8: PCM Interface Timing Specifications (Short Frame Synchronization, Master Mode)

Figure 10: PCM Interface Timing (Short Frame Synchronization, Master Mode)

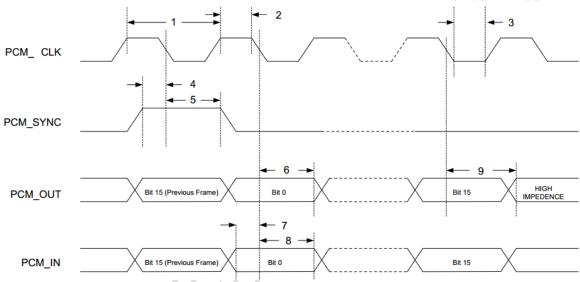

| Reference | Characteristics                                                                              | Minimum | Maximum | Unit |

|-----------|----------------------------------------------------------------------------------------------|---------|---------|------|

| 1         | PCM bit clock frequency                                                                      | 128     | 2048    | kHz  |

| 2         | PCM bit clock HIGH time                                                                      | 209     | _       | ns   |

| 3         | PCM bit clock LOW time                                                                       | 209     | _       | ns   |

| 4         | Setup time for PCM_SYNC before falling edge of PCM_CLK                                       | 50      | _       | ns   |

| 5         | Hold time for PCM_SYNC after falling edge of PCM_CLK                                         | 10      | _       | ns   |

| 6         | Hold time of PCM_OUT after PCM_CLK falling edge                                              | -       | 175     | ns   |

| 7         | Setup time for PCM_IN before PCM_CLK falling edge                                            | 50      | 77      | ns   |

| 8         | Hold time for PCM_IN after PCM_CLK falling edge                                              | 10      | -//     | ns   |

| 9         | Delay from falling edge of PCM_CLK during last bit period to PCM_OUT becoming high impedance | -       | 100     | ns   |

Table 9: PCM Interface Timing Specifications (Short Frame Synchronization, Slave Mode)

Figure 11: PCM Interface Timing (Short Frame Synchronization, Slave Mode)

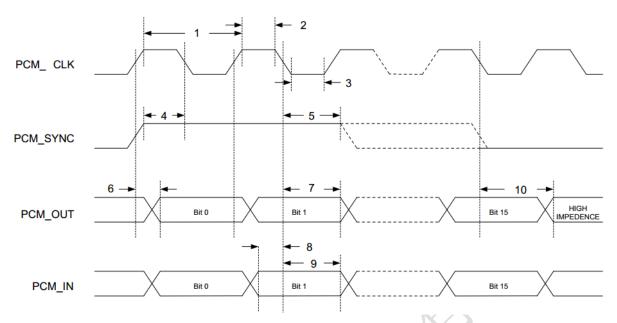

| Reference | Characteristics                                                                              | Minimum | Maximum | Unit |

|-----------|----------------------------------------------------------------------------------------------|---------|---------|------|

| 1         | PCM bit clock frequency                                                                      | 128     | 2048    | kHz  |

| 2         | PCM bit clock HIGH time                                                                      | 209     | _       | ns   |

| 3         | PCM bit clock LOW time                                                                       | 209     | _       | ns   |

| 4         | Delay from PCM_CLK rising edge to PCM_SYNC                                                   |         | 50      |      |

| 4         | HIGH during first bit time                                                                   | _       | 50      | ns   |

| 5         | Delay from PCM_CLK rising edge to PCM_SYNC LOW during third bit time                         | _       | 50      | ns   |

| 6         | Delay from PCM_CLK rising edge to data valid on PCM_OUT                                      | _       | 50      | ns   |

| 7         | Setup time for PCM_IN before PCM_CLK falling edge                                            | 50      | _       | ns   |

| 8         | Hold time for PCM_IN after PCM_CLK falling edge                                              | 10      | _       | ns   |

| 9         | Delay from falling edge of PCM_CLK during last bit period to PCM_OUT becoming high impedance | _       | 50      | ns   |

Table 10: PCM Interface Timing Specifications (Long Frame Synchronization, Master Mode)

Figure 12: PCM Interface Timing (Long Frame Synchronization, Master Mode)

| Reference | Characteristics                                                                                                                                          | Minimum | Maximum | Unit |

|-----------|----------------------------------------------------------------------------------------------------------------------------------------------------------|---------|---------|------|

| 1         | PCM bit clock frequency.                                                                                                                                 | 128     | 2048    | kHz  |

| 2         | PCM bit clock HIGH time.                                                                                                                                 | 209     | _       | ns   |

| 3         | PCM bit clock LOW time.                                                                                                                                  | 209     | _       | ns   |

| 4         | Setup time for PCM_SYNC before falling edge of PCM_CLK during first bit time.                                                                            | 50      | -       | ns   |

| 5         | Hold time for PCM_SYNC after falling edge of PCM_CLK during second bit period. (PCM_SYNC may go low any time from second bit period to last bit period). | 10      | _       | ns   |

| 6         | Delay from rising edge of PCM_CLK or PCM_SYNC (whichever is later) to data valid for first bit on PCM_OUT.                                               | _       | 50      | ns   |

| 7         | Hold time of PCM_OUT after PCM_CLK falling edge.                                                                                                         | _       | 175     | ns   |

| 8         | Setup time for PCM_IN before PCM_CLK falling edge.                                                                                                       | 50      | _       | ns   |

| 9         | Hold time for PCM_IN after PCM_CLK falling edge.                                                                                                         | 10      | _       | ns   |

| 10        | Delay from falling edge of PCM_CLK or PCM_SYNC (whichever is later) during last bit in slot to PCM_OUT becoming high impedance.                          | _       | 100     | ns   |

Table 11: PCM Interface Timing Specifications (Long Frame Synchronization, Slave Mode)

Figure 13: PCM Interface Timing (Long Frame Synchronization, Slave Mode)

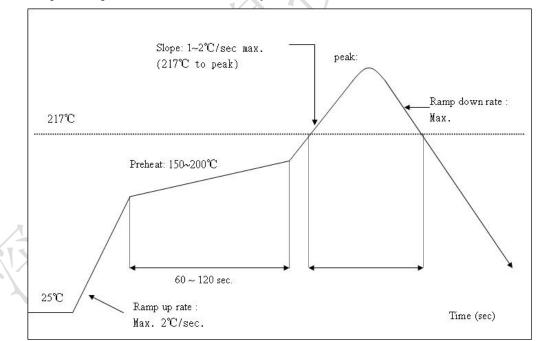

#### 10. Recommended Reflow Profile

Referred to IPC/JEDEC standard.

Peak package body temperature :<260 °C.

Time of peak temperature for Pb-free assembly: 5~10sec.

Figure 14: Solder Reflow Profile

#### 11. Electrical Characteristics

#### 11.1 Absolute Maximum Ratings

| Maximum Ratings     | Min   | Typical | Max    |

|---------------------|-------|---------|--------|

| Storage Temperature | -40 ℃ | /       | +125 ℃ |

| VBAT                | 3.0V  | 3.3V    | 3.6V   |

| VDD_PIO             | 1.7V  | -       | 3.6V   |

Table 12: Absolute Maximum Ratings

#### 11.2 Recommended Operating Conditions

| <b>Operating Conditions</b> | Min   | Typical | Max    |

|-----------------------------|-------|---------|--------|

| Storage Temperature         | -40 ℃ | /       | +105 ℃ |

| OperatingTemperature        | -40 ℃ | 20℃     | +85 ℃  |

| VBAT                        | 3.14V | 3.30V   | 3.46V  |

| VDD_PIO                     | 1.71V | 1.80V   | 1.89V  |

|                             | 3.14V | 3.30V   | 3.46V  |

Table 13: Recommended Operating Conditions

#### 12. PCB Layout Recommendation

#### 12.1 Antenna

Antenna trace impedance should be adjusted to 50ohm. The area above(or under)the RF antenna trace should be free from other traces.

#### 12.2 HCI UART Lines Layout Guideline

The following HCI line routing must obey the following rule to prevent overshoot/undershoot, as these lines drive  $4 \sim 8mA$

UART\_RX UART\_TX UART\_CTS UART\_RTS

The route length of these signals be less than 15 cm and the line impedance be less than  $50\Omega$

#### 12.3 PCM Lines Layout Guideline

The following HCI line routing must obey the following rule to prevent overshoot/undershoot, as these lines drive 4 mA

PCM\_SYNC PCM\_CLK PCM\_OUT PCM\_IN

The route length of these signals be less than 15 cm and the line impedance be less than  $50\Omega$ .

#### 12.4 Power Trace Lines Layout Guideline

VBAT Trace Width: 30milVDD\_PIO Trace Width: 20mil

#### 12.5 Ground Lines Layout Guideline

- A Complete Ground in Ground Layer.

- Add Ground Through Holes to GOC-BE470-V1.1 Module Ground Pads

- Decoupling Capacitors close to GOC-BE470-V1.1 Module Power and Ground Pads

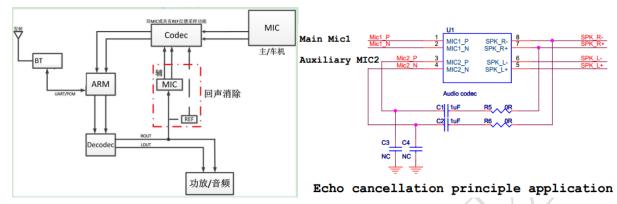

# 13. Echo Cancellation Principle

Figure 15: Sound Processing Flow Chart

The left picture is a schematic diagram of the echo cancellation principle. After Decodec decoding of the left and right channel sound, after data sampling and master MIC data comparison, echo cancellation can be processed. The right picture is a reference example, which can be designed according to the actual plan. Flying echo cancellation design, priority to use the echo cancellation design of IFLYTEK.

# 14. Module Part Number Description GOC-BE 47 0-V1.1 Company Name Module Package Reserved Module Version

Figure 16: Module Part Number Description

For a list of available options (e.g. package, packing) and orderable part numbers or for further information on any aspect of this device, please go to <a href="https://www.goodocom.com">www.goodocom.com</a> or contact the GOODOCOM Sales Office nearest to you.

# 15. Ordering Information

| Part Number    | Description      | Remark |

|----------------|------------------|--------|

| GOC-BE470-V1.1 | Bluetooth Module |        |

Table 13: Ordering Information

# 16. Packaging Information

#### 16.1 Net Weight

The module net weight:  $1g \pm 0.3g$

#### 16.2 Package

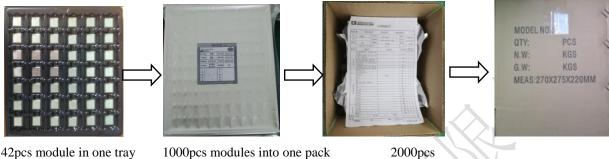

1000pcs modules into one pack

2000pcs

Modules One Box

Carton size:270mm\*275mm\*220mm

Tray size:208mm\*208mm\*9mm

#### 16.3 Storage Requirements

- 1) Temperature:  $22\sim28 \, \text{C}$ ;

- 2 ) Humidity: <70% (RH);

Vacuum packed and sealed in good condition to ensure 12 months of welding.

#### 16.4 Humidity Sensitive Characteristic

- 1) MSL: 3 level

- 2) Once opened, SMT within 168 hours in the condition of temperature:  $22 \sim 28 \, ^{\circ} \mathrm{C}$  and humidity<60%(RH).

- 3) Handling, storage, and processing should follow IPC/JEDECJ-STD-033